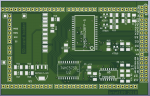

Первоначальная (оригинальная) схема доп. платы расширения внутренней SRAM микроконтроллеров на базе микросхемы HMM628512BLFP-5, емкостью 512 килобайт с временем доступа 50нс. На самом деле у значительного количества микросхем самых разных производителей статической памяти цоколевка SOP-32 корпусов имеет точно такую разводку ног и примерно те же самые тайминги. А, с учетом того что сюда вполне подходят и микросхемы памяти медленнее (3 такта ЦПУ микроконтроллера на цикл чтения/записи), то реальный выбор микросхем - "практически не ограничен" и их стоимость на момент покупки была в районе 40-60руб/корпус на АлиЭкспресс. Как итого, можно "придираться" к доп. параметрам, таким как "потребление в активном и пассивном режимах", возможность хранения с пониженным питанием, наличие встроенной батарейки для хранения при выключении .. и т.д. вплоть до поиска корпусов FRAM - ферритовой памяти, сохраняющей состояние длительно и вовсе без питания.

В общем - применимость весьма велика как и разнообразие поделок.

P.S. Изменения в схеме:

1. диод Д1, проводящий сигнал ALE на ногу CS чипа памяти - НЕ НУЖЕН и даже вреден. Его надо убрать, а входной сигнал EN подавать от дополнительной ножки микроконтроллера для "ручного" включения работы SRAM.

2. Подтягивать сигнал ALE к питанию - не надо!

3. На схему надо добавить резистор с базы на землю у Q1 не более 4.7к-9.1к, иначе он не закрывается полноценно.

4. Резистор R14 2.4к стоит уменьшить до 1к. В таком варианте, пауза для записи номера страницы получается около 45-90 тактов ЦПУ на 16Мгц. Чем меньше резистор с базы на землю - тем быстрее запирается этот транзистор. В целом некритично, поскольку это механизм переключения страниц..

Описание работы дистпетчера SRAM

1. Регистр-защелка U1 - строго согласно даташита занят демультиплексированием младшей части адреса ячейки А0-А7, в момент снятия сигнала ALE микроконтроллером. Ничем больше он не занимается и тут подходят только "быстродействующие" варианты типа 74HC573D или "быстрые" серии ACT, HCT и т.д.

Младшая часть адреса выведена на дополнительный интерфейс платы отдельно (см. средний прямоугольник).

2. Второй регистр (573D, U2) - регистр "страниц" ОЗУ. Хранит в младшей и старшей части текущие "номера страниц" от 0 до 15 и создает 2 "адресных пространства" по 256кб совместно с мультиплексором U3. Выбором подаваемой страницы на адресную шину ОЗУ управляет нога PortC бит6 (PC6, адресная линия А14) по входу S мультиплексора. Инвертированный транзистором сигнал адресной линии А15 (PC7) - принудительно переводит мультиплексор в третье состояние.

Поскольку его выходы подтянуты к питанию, это дает "фиксированный" адрес страницы на выходе, а именно последнюю №15.

Такое применение линий А14,А15, фактически разделяет адресное пространство микроконтроллера (64кб) на 3 окна:

"common window": А15==0, А14 - любое. Размер = 32кб. Расположение от 0 до 32кб.

"low window": А15=1, А14 = 0 - нижнее окно. На шину адреса ОЗУ выдается младшая тетрада регистра страниц. И из ОЗУ используется СВОЯ(!) половина памяти 256кб!

"high window": А15=1, А14=1 - верхнее окно. На шину адреса выдается старшая тетрада регистра страниц U2, и в ОЗУ используется вторая половина адресов, благодаря прохождению на адресную линию все того же сигнала А14!

3. Запись номеров страниц в регистр U2. Было замечено, что в даташите нигде(!) одновременно не используется 2 низких сигнала на линиях WR,RD! Этот факт и положен в основу записи номеров страниц ОЗУ в регистр с той же самой линии данных: При обоих низких сигналах диодно-транзисторной ИЛИ-НЕ схемой (D3,D4,Q1) разрешается прохождение шины данных в регистр и по снятию любого из них - происходит фиксация номеров страниц в регистре. Просто, дешево и сердито.

Управление записью номеров страниц в регистр производится библиотекой "вручную", при отключенном режиме "внешнего ОЗУ". При этом, чтобы не происходило дополнительной ложной записи в ОЗУ сигнал EN должен быть переведен также в закрытое состояние силами ПО.

Итого, имеем страничный диспетчер ОЗУ емкостью на 512килобайт, который предоставляет программам нижнее, общее и единое (не перепрограммируемое) окно в 32 килобайта, часть из которого занимает внутреннее ЗУ микроконтроллера. Кроме этого, предоставляется 2 окна по 16килобайт с возможностью "листания" страниц ОЗУ размером по 16кб, также НЕ пересекающихся между собой. Например страница №3 нижнего блока никак не доступна в расположении в верхнем окне адресного пространства ЦПУ. При статической линковке адресов это "аппаратно" исключает возможность "кривой адресации" из-за перемещения страницы ЗУ "чисто физически".

Ну вот. Нашел пока это..

Изменено: